PAGE CONTENTS

Objectives

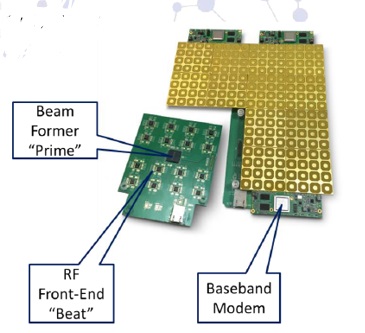

This project covers the development of a Digital Beam Former ASIC (PRIME) that enables the next generation of multi-beam, steerable phased array antenna. The PRIME device enables the creation of phased array antenna where signal processing or conditioning occurs within the digital domain. This will be used for both the receive and transmit operation of the satellite signal. Scalable architecture caters for the different market segments with support for varying bandwidth and power requirements.

Challenges

The key challenge is to come up with low-cost, low-power, high-performance modular design that is scalable and supports a wide range of features.

System Architecture

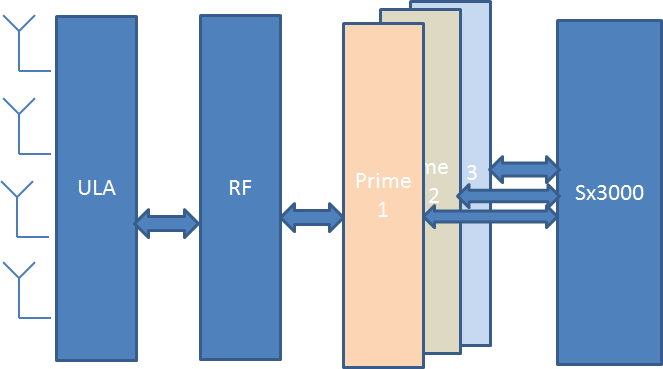

In this project, digital beam forming ASIC chip (PRIME) will be designed. A top level architecture is given below. Satellite Modem (Sx3000) can control multiple digital beam forming Prime Chip. Each of the Prime chips is connected to set of RFIC and Antenna Elements.

On the receive side, signals from each antenna elements are combined in PRIME coherently and passed onto Satellite Modem for demodulation. On the transmit side, IQ from Modem is processed in Prime ASIC and coordinated across Prime to do beam forming. Architecture is designed to be able to handle multiple beams.

Plan

The project is planned in 2 phases.

Phase-1 is focused on achieving Tape Out of the Digital Beam Forming ASIC Chip. There are 3 milestones in this phase-1.

PDR (Primary Design Review) – System Specification ready

CDR (Critical Design Review) – RTL code is reviewed & frozen.

Tape-Out Review – Design as GDS sent to FAB for production.

Phase-2 is focused on validation of the chip. There are 2 milestones in this phase-2.

MPW Review – Evaluation Board & Post Silicon Test Plan ready.

Benchmark Results Review – Transmit & Receive Beam forming benchmark results are ready.

Current Status

The project has reached Critical Design Review Milestone. System design and ASIC specification have been completed. ASIC design is well underway with RTL code and validation in progress. ASIC package options and the evaluation board design are kicked off.

Companies