PAGE CONTENTS

Objectives

Development of efficient digital beamforming algorithms: The activity focuses on developing low-complexity and highly efficient digital beamforming algorithms for satellite communication payloads based on digital processors, with the objective of reducing implementation complexity while maintaining flexibility and performance.

Exploitation of beam and array symmetry: Mathematical techniques exploiting the spatial symmetry of both the beams and the radiating elements are investigated to simplify the processing chain. This approach aims to reduce the required operations to a set of additions and subtractions, and in many cases to avoid multiplication operations entirely.

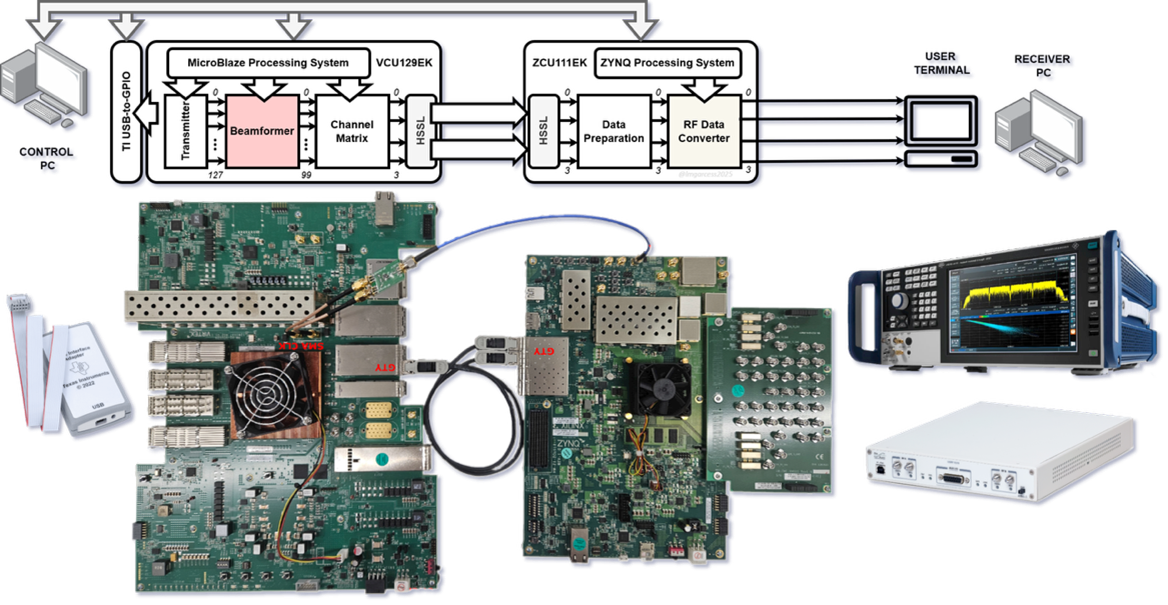

Representative digital processor testbed: A representative digital processor testbed is developed to implement and validate the proposed algorithms and processing techniques under realistic conditions, providing a practical demonstration of their feasibility.

Reduction of power, mass, and hardware complexity: The activity targets significant reductions in power consumption, mass, and volume, while also improving integration efficiency. In particular, it aims for a 50% reduction in power consumption and a 50% reduction in the number of ASIC/FPGA components compared with current digital beamforming implementations.

Advancement toward flexible high-capacity payloads: The activity is intended as an enabling technology for the development of highly flexible, high-capacity digital payloads based on large antenna arrays, increasing their practical readiness for future SATCOM systems.

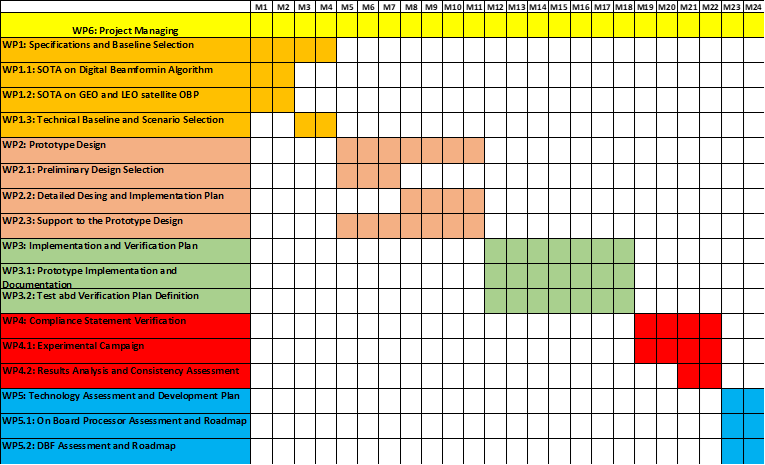

Technology Readiness Level (TRL) increase: The activity aims to raise the Technology Readiness Level from TRL 2 to TRL 4 through algorithm development, implementation, and validation on the representative processor testbed.

Challenges

High-computational complexity of digital beamforming: Conventional digital beamforming for large SATCOM antenna arrays requires a high number of operations, particularly multiplications, which leads to substantial processing complexity and limits efficient real-time implementation.

Power consumption constraints in on-board processing: Digital beamforming implementations based on current processing architectures can consume significant power, which is a major challenge for satellite payloads where power resources are limited.

Mass, volume, and integration limitations: The use of multiple ASICs/FPGAs and associated hardware increases the mass, volume, and integration complexity of the payload, making the implementation of highly flexible digital beamforming architectures more difficult.

Scalability to large array antennas: As the number of antenna elements and beams increases, the processing requirements grow rapidly. Ensuring scalability while maintaining manageable hardware complexity is therefore a key challenge.

Efficient exploitation of spatial symmetry: Although the spatial symmetry of beams and radiating elements offers strong potential for simplification, translating these mathematical properties into practical low-complexity algorithms and architectures remains challenging.

Validation on representative hardware: Demonstrating the feasibility of the proposed techniques requires implementation and testing on a representative digital processor testbed, which is essential to bridge the gap between theoretical development and practical applicability.

System Architecture

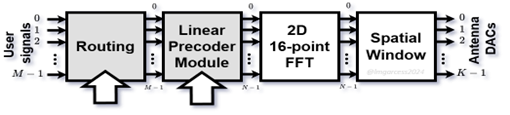

The proposed system is a 2D FFT-based digital beamforming architecture designed for efficient implementation in SATCOM payloads. The processing chain starts with a routing stage, which dynamically maps user signals to the beamforming network. This routing is based on a Benes Permutation Network (BPN), enabling flexible user-to-beam assignment with low power and logic usage.

After routing, the signals are processed by a linear precoder module, where a sparse matrix is used to reduce resource consumption. The precoding stage is organized in clusters, allowing local precoding and significantly decreasing DSP usage compared with conventional implementations.

The precoded signals are then fed into a 2D 16-point FFT block, which performs the core beamforming operation. Two implementation options are considered for this stage: a non-quantized twiddle-factor version, which provides higher precision at the cost of DSP usage, and a quantized twiddle-factor version, which removes DSP dependence and enables hardware resource savings. Trade-off analysis shows that quantisation, rounding, truncation, and bit-width selection directly affect the resulting SNR and must therefore be carefully optimised.

Following the FFT stage, a spatial windowing block is applied to shape the beam pattern and improve coverage control. The overall architecture is implemented on a fixed 10×10 subarray, which reduces the number of antennas and RF chains while making efficient use of payload resources. In addition, the use of overlapping beams allows the system to extend coverage beyond the strict uniform FFT grid and to address more general, non-uniform service areas through appropriate beam combination.

Plan

Current Status

TAR Finalised.