PAGE CONTENTS

Objectives

This project covers the development of true time delay digital beam former demonstrator with 64 antenna elements operating in Ku band.

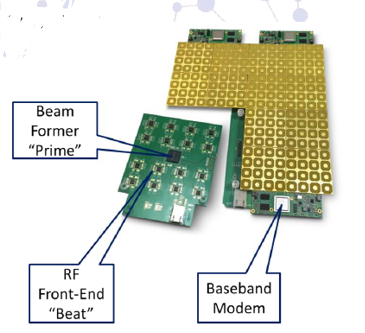

The demonstrator will have 4 main parts – Satellite Modem, Digital beam former ASIC, Ku band RFIC & Antenna elements. Ku band RFIC, antenna elements and Integrating the 4 main parts are the focus of this project.

Challenges

The key challenge is to come up with low-cost, low-power, high-performance modular design that is scalable. Other significant challenges are generating & distributing LO, integrating Beat RFIC & antenna elements on PCB and the cost-effective antenna design.

System Architecture

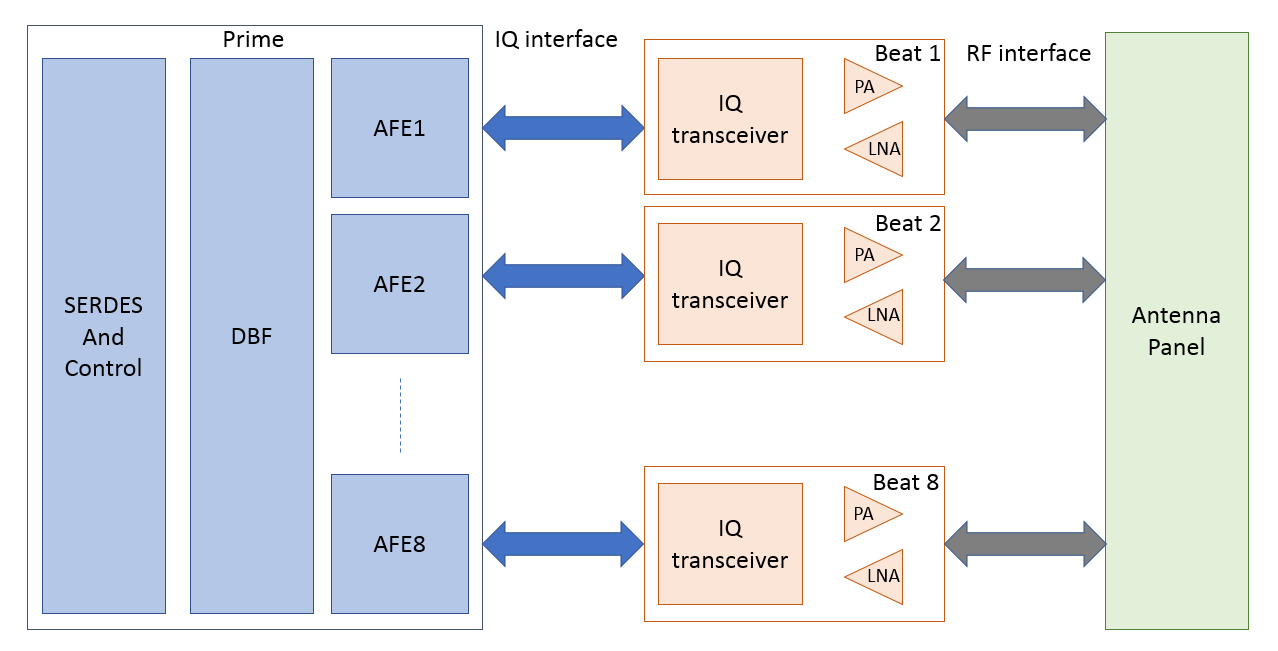

RFIC (Beat) is an analog transceiver that converts baseband (IQ) from the digital beam forming ASIC (Prime) to Ku band antenna panel and vice versa. Each Beat RFIC has 4 IQ transceivers and can connect to 4 antenna elements. We can increase the number of Beat RFIC chip as per the number of antenna elements making the architecture modular and scalable. In the below diagram we see single digital beam forming chip (Prime) supporting 8 Beat chip that connects to 32 antenna elements. Flexibility is also available in configuring all 32 antenna elements as Rx only or Tx only or split them as 16 for Rx & 16 for Tx.

For the IOT demonstrator, 2 Prime chips with 16 Beat RFIC chips (Ku band) and 64 antenna elements are planned to be integrated along with one satellite modem ASIC.

Plan

The project is planned in 2 phases.

Phase-1 is focused on achieving Tape Out of the RFIC Chip. There are 3 milestones in this phase-1.

Phase-2 is focused on validation of the chip and the demonstrator hardware.

Current Status

The project has reached RevA0 RFIC Tape-Out design review Milestone. System architecture and RFIC requirements are completed.

Companies