-

StatusCompleted

-

Status date2025-10-29

-

Activity Code4F.106

The project objectives of the DPC G1 development are:

- Formally qualify the Digital Programmable Controller ASIC (DPC-G1) developed under the previous ARTES-5.2 contract;

- Develop both hardware and software test environments necessary for comprehensive qualification;

- Execute all the required qualification steps according to the ESCC9000 standard, ensuring the ASIC meets flight model (FM) quality requirements;

- Validate the DPC-G1 ASIC's performance and radiation hardness as demonstrated in earlier prototype testing and integration in avionic equipment.

The ARTES 3-4 contract, according to ECSS 9000, was successfully completed in February 2017, and serves as the follow-on to the project whose key deliverable was a DPC G1 prototype. This prototype, along with the software development toolkit, was successfully tested for performance and radiation within the initial phase.

The major challenges during the development of the DPC were:

- The project involved extensive qualification and testing activities, including the development of hardware and software test benches to ensure smooth and efficient qualification. The tests were conducted according to ESCC 9000 standards, which are stringent requirements for space-grade components;

- Keep the production yield at a high level without compromising the test coverage or the performance;

- These challenges highlight the complexity of developing and qualifying space-grade technology, ensuring cost-effectiveness, and adapting to different application domains;

- The management of a complex ecosystem with key subcontractors (IMEC and ICSense) and many suppliers.

The DPC brings a cutting-edge solution for all satellite equipment requiring digitalisation thanks to a microcontroller. Thanks to its fine-tuned feature list, the DPC allows an efficient decentralisation lowering interruptions and communications with OBC.

The component is RadHard by design, its supply chain is under TAS control without US content.

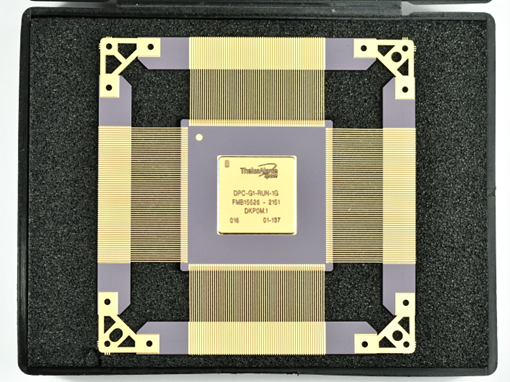

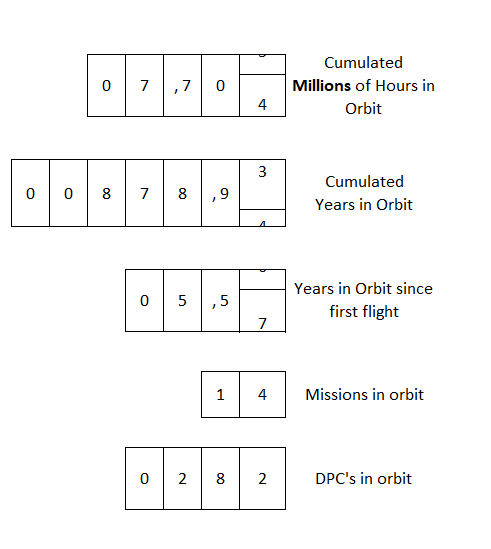

The DPC has already been embarked in a large perimeter of applications and missions in different domains (satcom, observation, navigation and exploration / science). The flight heritage data speak for themselves.

- Total dose: no drift up to at least 60kRad(Si);

- SEL Hardened > 68 MeV.cm²/mg;

- SEU Hardened > 40 MeV.cm²/mg;

- -55°C to +125°C Operating Temperature Range;

- Reliability 22..29 FIT (65°C junction T°)

- Six independent PWM with complementary outputs

- 16 ADC inputs, 3 DAC outputs, 108 digital IOs

- Low power 120…600 mA @ 3.3V

- Function Segregation for “mission critical” use

- Up to 3 x ~30 MIPS total processing power

- On-chip bandgap and PLL

DPC Si RadHard by design, intensively RAD Tested (more than 100 hours in Cyclotron) and does not include any US content.

By architecture, the DPC is a multipurpose multi-mission RadHard microcontroller.

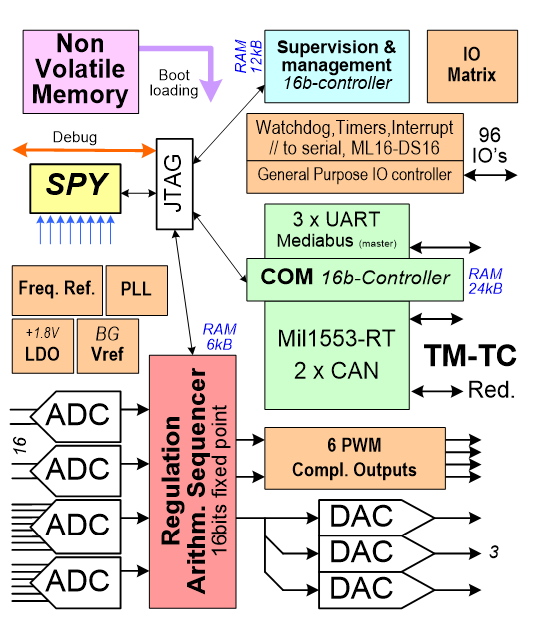

The DPC is a mixed-mode “system-on-chip” integrating a very large set of functions present in space equipment for the management of sensors, actuators, power systems, multiple communication protocols, etc.

Next to main controller functions, all servicing functions are present on the silicon die such as power supplies (LDO), clock oscillators, reference voltages, non-volatile e2prom management, initialisation and self-test features (not represented on figure). It only requires a +3.3V supply with some passive decoupling component and its serial non-volatile memory to operate.

The DPC concatenates three applicative controllers in one chip: (so-called) SSM, COM and RAS controllers. Although they are located on the same die, each of these 3 controllers has its own CPU. Consequently, they operate independently from each other increasing the determinism of each process that is taking place. Tasks can be orthogonal to each other with strongly simplified interruption scheme. The DPC is mostly used without operating system as sufficient processing resources are available to manage multiple tasks fully in parallel.

The DPC integrates a large variety of peripherals and hardware accelerators such as ADC, DAC, PWM generators, timers, SPI, I2C, UART, mil-1553 bus, CAN-bus, hardware 32 bits MACC, hardware 32 bits divider and barrel shifter.

To support software development, each CPU is equipped with trace and debug hardware. A centralized SPY system supports transparent and non-intrusive process monitoring and debug. Software development suite mostly relies on worldwide standards such as GCC (compiler) and GNU debugger. Together with specific tools for code upload, E2prom programming and non-intrusive debug, these tools are integrated into the Eclipse environment.

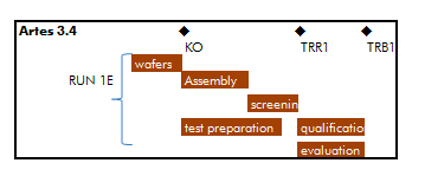

This figure gives an overview of the different activities performed during project plan execution.

Completed.

DPC (run 1E) is successfully qualified according to ESCC9000. All hardware and software developments for the test environment to support qualification have been developed and formally accepted.