PAGE CONTENTS

Objectives

-

The primary objective of the proposed activity is to develop and test a new generation microcontroller GR716B based on the GR716A microcontroller. GR716B shall enable use of commercial off the shelf (COTS) FPGAs in critical space applications (beneficial not the least for satcom constellations), support switching power applications, enhance analogue functions, increase processing performance and support more advanced interfaces.

-

The secondary objective of the proposed activity is to extend existing GR716A Software Development Environment (SDE) from TRL 4 to TRL 6 for GR716B and porting of Zephyr RTOS to GR716B. The extension of the Software Development Environment includes software driver support for new functionality (BCC2), extending and optimizing the instruction simulator (TSIM3) and graphical debugger (GRMON3) support for the GR716B microcontroller.

Challenges

-

Ensure that the package design changes are not affecting functional or performance of existing or new functionality.

-

Ensure that the evaluation board design is possible to use for validation of new functionality.

-

Ensure no errors in the integration of new digital functions and interfaces.

-

Ensure no errors in the integration of new analogue functions and interfaces.

-

Ensure that the Analog performance are met in all process corners or over full temperature range

System Architecture

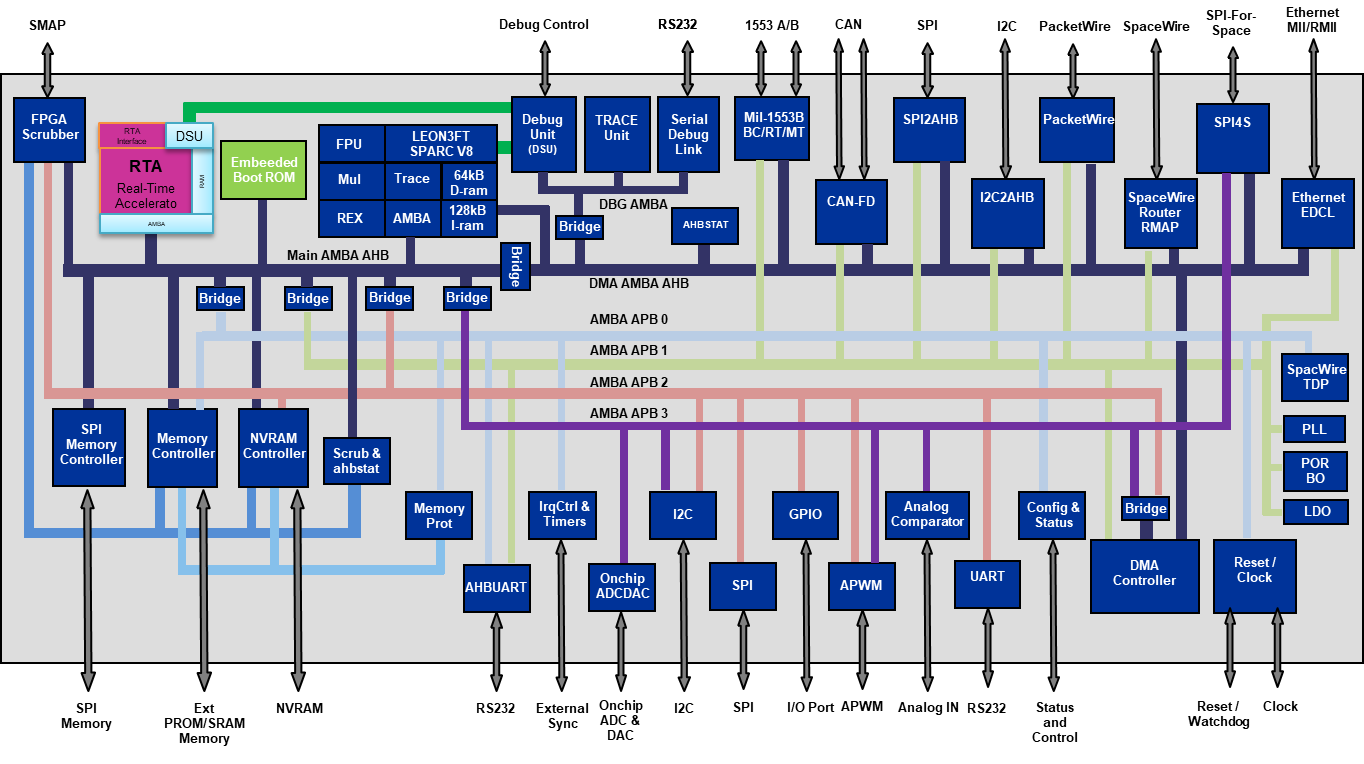

The figure below illustrates the architecture for the entire product.

-

• Fault-tolerant SPARC V8 processor with 31 register windows, 192KiB EDAC protected tightly coupled memory and support for compressed instruction set.

-

• Double precision IEEE-754 floating point unit

-

• Memory protection units

-

• Non-intrusive advanced on-chip debug support unit

-

External EDAC protected 8-bit PROM/SRAM, SPI memory protected by EDAC and dual memory redundancy

-

Hardware FPGA programming and scrubbing • Real-Time Accelerators and programmable DMA

-

SpaceWire router with 2 external ports and time distribution

-

MIL-STD-1553B interface

-

CAN FD interface with CANOpen support

-

PacketWire with CRC acceleration support

-

Programmable PWM interface with Digital voltage control and motor control loop support

-

Programmable pulse-width-modulation DAC

-

SPI with SPI-for-Space protocol support

-

On-chip four channel 12-bit DAC, four 13/14-bit ADC and fast analogue comparators

-

10/100 Ethernet, UARTs, SPI, I2C, GPIO, Timers with Watchdog, Interrupt controller, Status registers, UART debug, etc.

Plan

The project consists of the following major work packages and milestones:

-

WP100 Digital Design modification

-

MS1 Detailed design review

-

WP200 Analog Design update and Layout support

-

WP400 Package design

-

MS2 Critical design review

-

WP300 Preparation, prototype and die manufacturing

-

WP500 Production test development and preparation

-

WP600 Package assembly and test

-

WP700 SDE development and RTOS porting

-

WP800 Test plans and specifications

-

WP900 Evaluation board development and validation

-

MS3 Test readiness review

-

WP1000 Validation of ASIC

-

WP1100 Validation of Switching Power Regulators

-

WP1200 Project management

-

MS4 Final review

Current Status

The project has finished the Technology phase. An updated Data Sheet has been published.