PAGE CONTENTS

Objectives

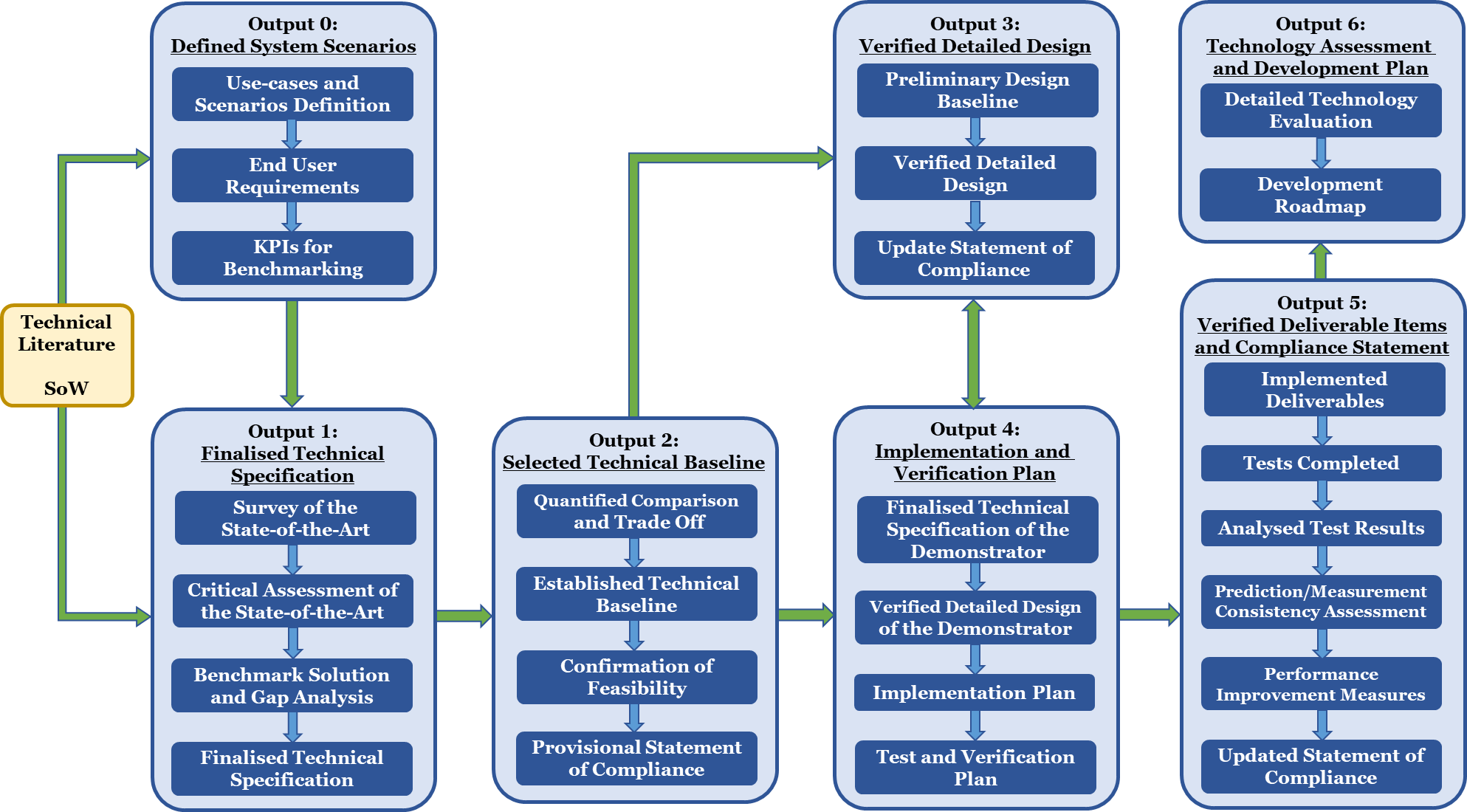

The objective of this Project is to create a breadboard of an integrated wideband multiplexer, supporting both terrestrial and satellite 5G communication, to perform a first validation of the related enabling technologies. The activity includes a first phase which foresees the study and definition of possible scenarios and use cases which benefit from the exploitation of this innovative technique.

The activity includes a first phase which foresees the study and definition of possible scenarios and use cases which benefit from the exploitation of this innovative technique.

In parallel, the Technical Specifications of the system are defined.

The Activity proceeds with the analysis of possible technologies which, after a trade-off analysis performance and complexity lead to the selection of a Technical Baseline. This represents the starting point for the system design phase, which considers both the design of a MMIC device and of a breadboard for its validation. The design is assisted by the definition of an Implementation Plan and a Validation Plan, which includes a first functional verification on the MMIC device and then a detailed verification after its installation on the breadboard.

The outputs of the validation phase allow to identify a set of technological gaps with the objective to propose possible improvements and enhancements to increase the TRL of the system in view of its possible commercialization / industrialization.

Challenges

The challenging issue of this project concerns the need to optimize the RF performances of the system, in particular the insertion loss, the related passband ripple and rejection margins, while maintaining the order of the filters limited. The final solution shall guarantee an adequate level of matching both at the input and the output interface. The design shall maintain reduced the design/implementation complexity, compatibly with the realization of 3 channels of filters (low-band, mid-band and high-band) in monolithic technology.

System Architecture

The overall system consists of 2 main sub-systems, which are integrated to handle the operations.

-

MMIC wideband multiplexer, which represents the focus and the main innovative output of the Activity.

-

Breadboard for testing, which is developed to allow the characterization and validation of the MMIC multiplexer during the Test Campaign, and is designed with the objective to perform RF measurements and derive the performance parameters of the multiplexer.

More in detail, the MMIC Multiplexer is in turn be composed of 3 RF channels, representing a low-band filter, a mid-band filter and a high band filter. Each channel is represented by its specific design and technology, which is determined with the objective to optimize the expected performance.

Output and Input interfaces are developed to integrate the MMIC multiplexer with the Breadboard and with the external environment (laboratory instrumentation and equipment) to perform the full validation tests.

The system architecture in represented in the high level description schematic reported in the following figure.

Plan

The project foresees the following Milestones (MS).

MS1, upon successful completion of WP2, expected by November 2023. MS2 at the end of WP4 activities, due in May 2024. Positive conclusion of WP5 activities lead to MS3, planned for December 2024. Upon the Agency’s acceptance of all deliverable items due under the Contract and the Contractor’s fulfilment of all other contractual obligations, the final Milestone MS4 is expected to be fulfilled by September 2025.

Current Status

The Activity started on July 2023. The Milestone MS1 has been completed in December 2023. Team is currently performing the activities of WP3: Design of the Multiplexer and the Demonstrator