PAGE CONTENTS

Objectives

Phase noise is a key parameter in frequency converters used on-board telecom satellites. This relates directly to the performance of the local oscillators (LO).

Local oscillator performance is limited when conventional integer-N synthesizers are used within a minimum step equal to the reference frequency. Fractional-N synthesizers overcome this limitation, allowing a step size reduction and therefore higher payload flexibility. However, fractional-N synthesizers typically suffer from a high level of undesired spurious products.

It is believed that architectures based on a combination of a fine frequency step reference synthesizer (e.g. DDS) and a coarse step PLL with a relatively high phase compensation frequency will alleviate these problems.

SYSTEM ARCHITECTURE

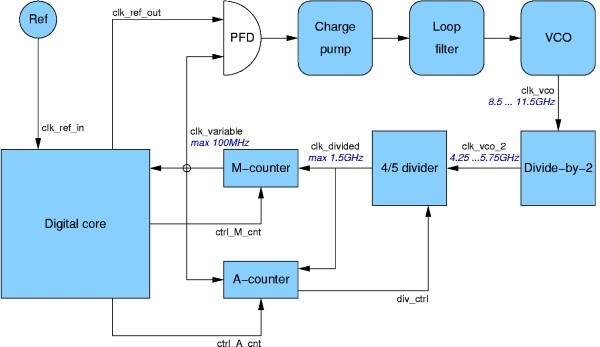

The picture below shows the architecture of the Synthesizer Chip. Key components are VCOs with very low phase noise and an accurate PFD and charge pump combination. Counter (M/A) and 4/5 divider are realized with bipolar elements (ECL) to handle the high input frequency of the feedback path. The divider ratio is controlled by CMOS logic including a sigma delta modulator (SDM), which provides a Gaussian distribution of the division ratios in order to allow fractional dividing at moderate spur and quantization noise levels. Output frequency generation in 10 mHz step size is possible by that.

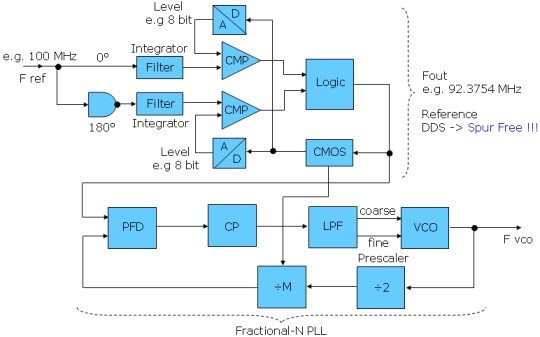

While operating in fractional mode with divider settings close to an integer value, the generation of ‘integer-N boundary’ spurs becomes dominant. Expanding the fractional part is possible by employing a second reference frequency – or moving the existing reference away from its nominal value. The reference frequency shift is subject of the circuitry sketched below.

Challenges

Due to lag of filtering, limited isolation and high design density, especially integrated system on chip solutions may cause unwanted spurs and worse phase noise performance, which harm the overall bit error rate. Achievement of superior results beside the known limitations is one of the most challenging tasks within this project.

Plan

The project is divided into two phases. Phase 1 deals with requirements, architectural design and block model validation. In phase 2 the novel synthesizer and reference tuning part will be designed, laid out, manufactured and tested. Two manufacturing cycles are planned in phase 2.

Current Status

Redesigns of the synthesizer chip and reference frequency tuning component have been manufactured and evaluated. The synthesizer chip was improved further regarding phase noise and frequency tuning range, due to adaptions on the PFD/CP complex and the VCOs. The reference frequency tuning part got additional testability and an improved overall setup, but did not gain in respect to its phase noise performance. Measurements show, that all components within the generator cores contribute to the overall phase noise. While improvements might be possible, realizing the necessary low level of phase noise cannot be guaranteed.

Summarizing it can be said that the NOVELO was a huge success.

IMST intends to sell the NOVELO chip for both, industrial and space purposes. Currently, IMST is discussing a possible qualification of NOVELO with DLR, Germany.

Companies