PAGE CONTENTS

Objectives

Phase noise is a key parameter in frequency converters used on-board telecom satellites. This relates directly to the performance of the local oscillators (LO).

Available market components show promising phase noise results but a limited frequency range. Mainly based on GaAs, their requirement of chip size is large and the connectivity to an external PLL mandatory.

The proposed SiGe VCO array solution can easily be integrated with complete PLL resulting in a 1-chip integrated synthesizer from 1.5 to 12 GHz. To our knowledge, comparable devices are not available on the market today, especially not as a radiation hard flight component.

Benefits

Significant payload reduction is the main advantage of single chip solutions with a high level of integration in comparison to hybrid setups. Beside the economy of space, decreased price, assembly time, and power consumption can be expected.

In addition, re-configuration of the system for different frequencies is possible without limitations in signal quality, which offers superior flexibility compared to all other solutions.

Challenges

Main challenge is the very low phase noise of the VCO array in combination with the large bandwidth. However, IMST demonstrated already a comparable performance on IHP SGB25V process within the NOVELO project. Also, the exact fine tuning of the VCO frequency ranges is demanding and needs detailed investigation due to inductive parasitic effects within the oscillator cores. 3D field simulation tools, e.g. EMPIRE or ADS MOMENTUM, will be used to cover that topic.

System Architecture

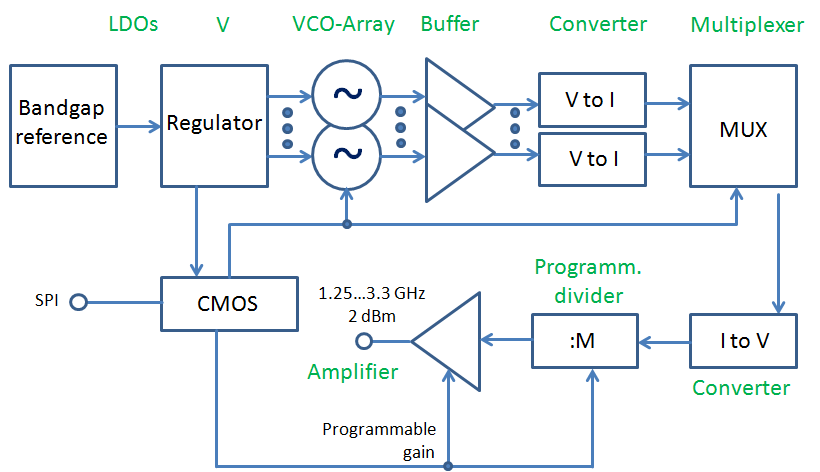

The picture below shows the architecture of the VCO array in combination with the required environment. While the key components are the VCOs with very low phase noise, which are intended to cover a frequency range from 6 to 12 GHz, the use of additional dividers expand the valid frequency range down to 1.5 GHz. The VCO array will be multiplexed to a single output, divided if necessary and amplified via PA finally. VCO settings, divider ratio and peripheral settings are controlled by CMOS logic via SPI, but can be applied also directly from off-chip to bypass radiation effects. The local voltage supplies are generated on-chip by LDOs employing bandgap references, which are very insensitive regarding voltage and temperature variation.

Plan

The project is divided into two phases. Phase 1 covers a technology and concepts review as basis of the preliminary and detailed VCO array design. In phase 2 the designed chip component will be manufactured, evaluated and redesigned. Two manufacturing cycles are planned in phase 2.

Current Status

Within this project an octave covering VCO array was developed, covering the complete frequency range from 1.5 GHz to 12 GHz. Furthermore, PLL functionality was added to the VCO array, resulting in a full functional fractional-N synthesizer with excellent phase noise behavior.

Beside those achievements some remaining issues must be addresses outside the frame of this project:

Even with very careful design of the VCOs, including adaption of IHP design-kit elements and EM-modeling of parasitics, there still is the need of improvements in respect to the temperature behavior of the VCOs for covering the complete temperature range.

Another important topic is the optimization of the RF output chain, with too much gain at lower frequencies causing RF noise and a temperature dependent gain slope to higher frequencies. In combination with the 3rd stage adaption of the output amplifier an overall output power of about 5 dBm should be achievable.

Covering the frequency range above 12 GHz is also of interest. Improvements of the times two multiplier input power will result in a larger operational band width of the synthesizer.

Finally, further higher SET of the design is intended. Laser tests have provided options to improve the SET of the synthesizer to values of approximately 50 MeV cm²/mg.

Currently, IMST is qualifying the NOVELO synthesizer including the SORA VCO array with the help of DLR, Germany.

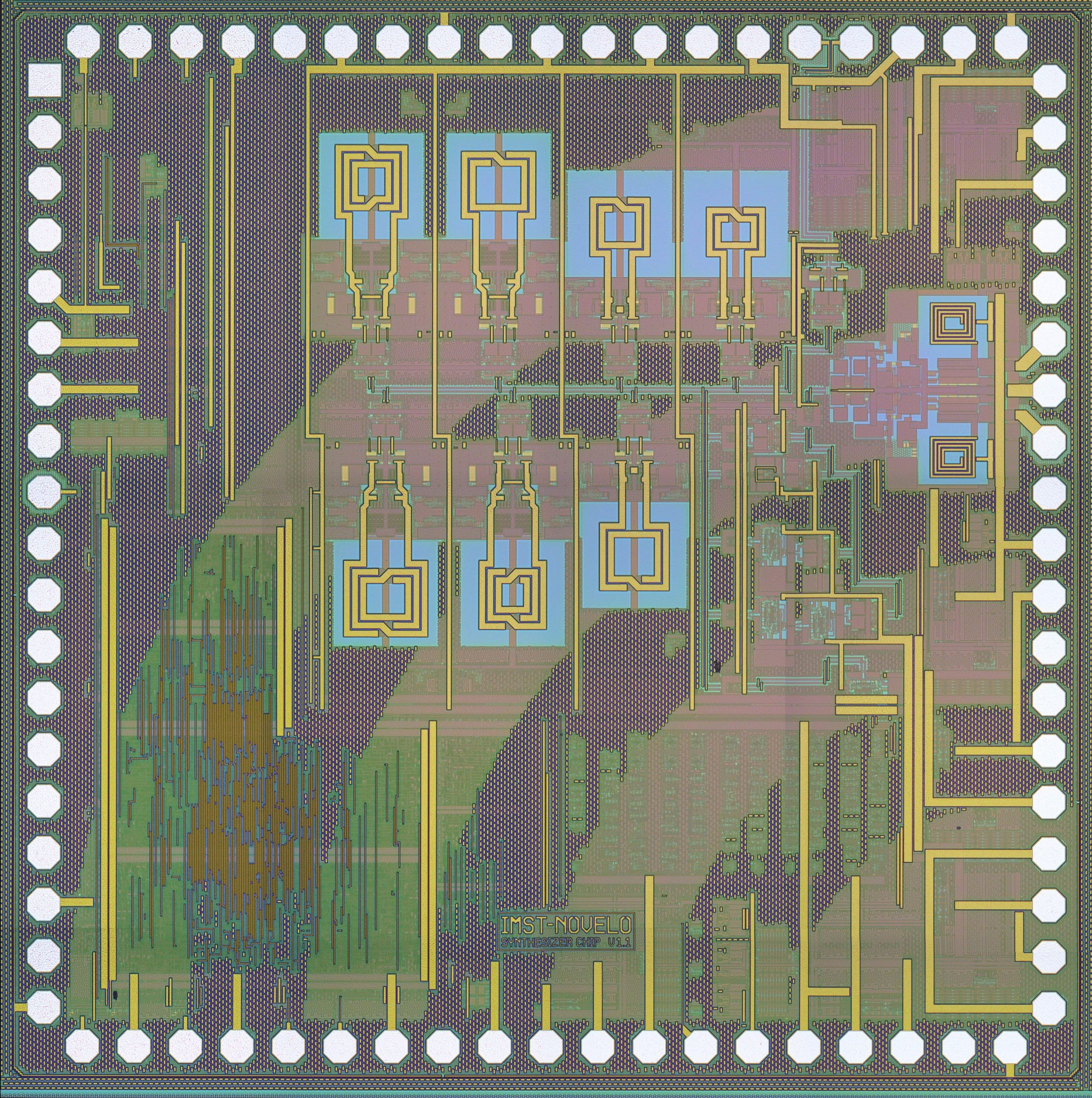

Chip photograph of the latest NOVELO synthesizer v1.1.

Companies