PAGE CONTENTS

Objectives

The objective of this project is to develop a new Software Defined Radio (SDR) platform specially designed for the implementation of high-end satellite communication applications. The new platform is modular, with a carrier board having the capability of plugging powerful FPGA SoC modules and radio front-end modules and high-speed DACs and ADCs into FMC+ connectors.

In the photo below, the carrier board is mounted in the 19” rack mechanical enclosure.

The FPGA SoC module developed in this project can be seen in the photo below.

Challenges

Key challenges of the project are:

- Complex PCB layout of the FPGA SoC processing module where the need for interconnecting large amount of DDR4 RAM to the SoC FPGA must be balanced against the need for a large number of high-speed transceiver lines in a small PCB area

- High speed transceiver interconnects via 2 x FMC+ connectors between FPGA SoC ICs and between FPGA SoC ICs and high speed ADCs, DACs and Ethernet fibre interfaces

- Implementation of a flexible software framework to automate the generation of the management interfaces of the applications running on the platform

System Architecture

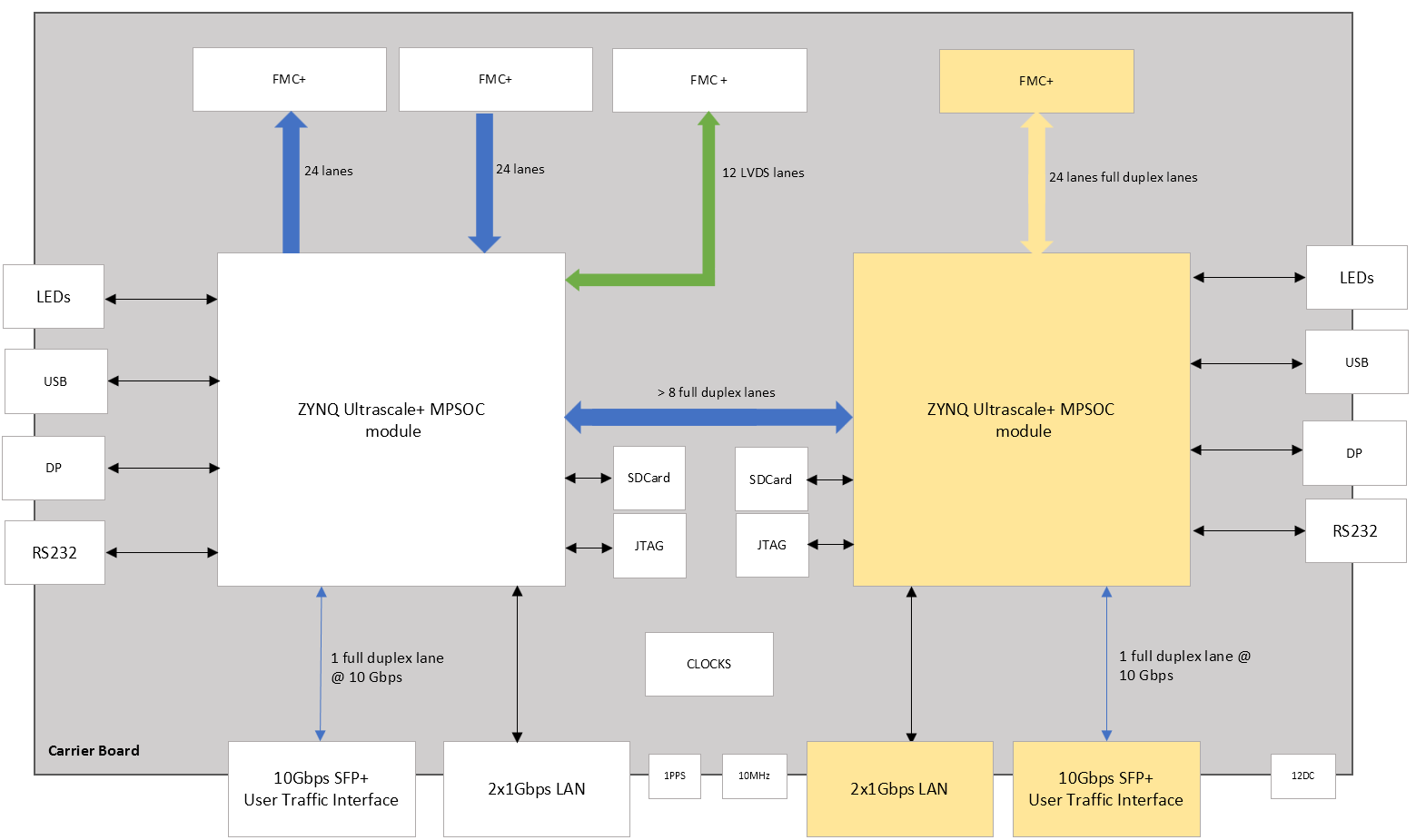

The block diagram below illustrates the top level architecture of the SSDR processing platform. The platform consists of a carrier board with one, or optionally two, SoC FPGA processing module(s) mounted. The yellow blocks in the block diagram are only available when the second SoC FPGA module is mounted. The platform is designed to be as generic as possible, to be compatible with new ADCs, DACs, and radio front-end modules that will enter the market in the coming years. The SoC FPGA module is built around the Xilinx Zynq UltraScale+ SoC EG family, and the PCB design supports the ZU11EG, ZU17EG, and the ZU19EG devices. The primary SoC processing module is connected to multiple FMC+ connectors that support ADCs, DACs and narrow band receiver mezzanine boards. The carrier board provides the main 10Gbps SFP+ interface, the dual LAN interface as well as the USB, display port and serial debug interface.

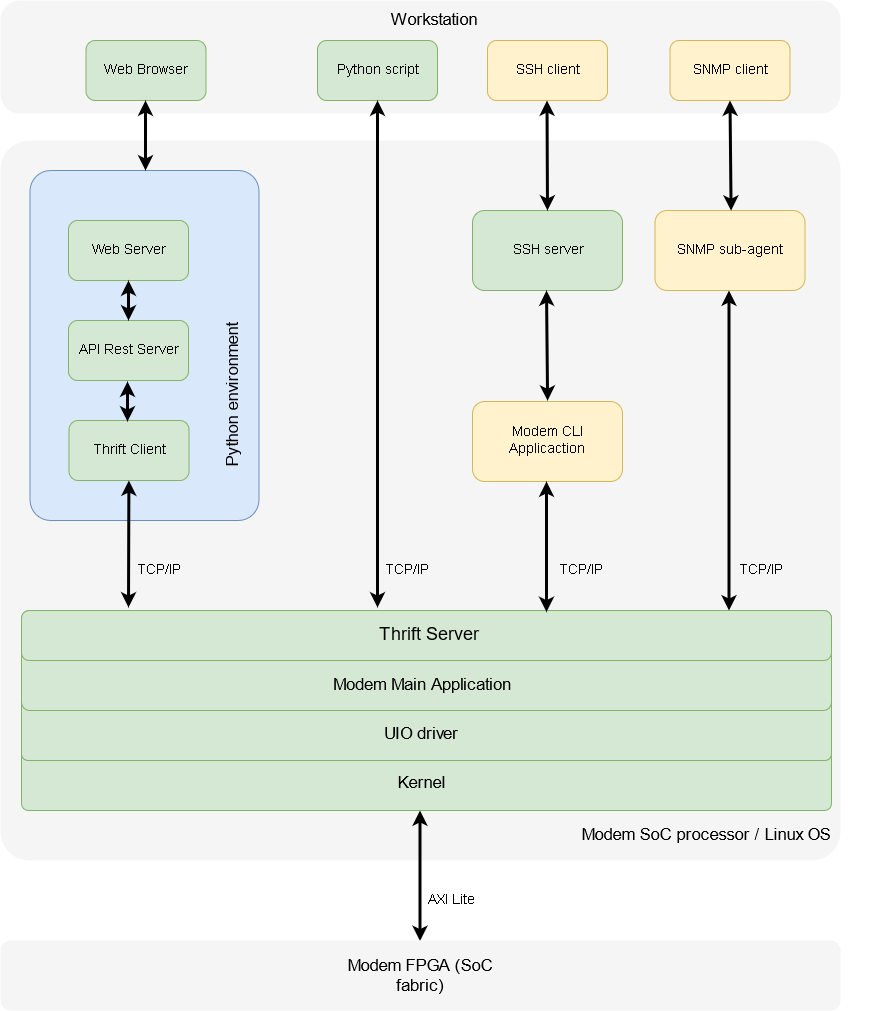

In the project, a SW tool referred to as the Interface Generator (IG) is developed in Python. The main focus is to generate a Web Interface for regular user interaction and a Python interface for automating the testing of the applications running on the SDR platform. In addition, to simplify documentation and ease generation of software code for management interface, an Interface Control Document is generated automatically in the process.

The figure below offers an overview of the management interfaces and SW stack developed in this project for the SDR platform.

Plan

- Kick-off: November 2017

- Design Review (DR): February 2018

- Acceptance Test (AT): September 2019

- Final Review (FR): October 2020

Current Status

The development of the new SDR platform was completed in September 2019, and the first unit was delivered to a customer in the second quarter of 2020.

Example of applications that have been implemented and demonstrated on this new SDR platform are:

- 5 Gbps, 1400 Msps DVB-S2X Satellite Modem

- 1500 MHz satellite channel simulator for Low Earth Orbit

The final review of the project was carried out in October 2020.

Companies