PAGE CONTENTS

Objectives

The aim of the project is the implementation of a fully software defined DVB-S2X demodulator, running on general-purpose hardware, which could replace a dedicated hardware demodulator in some selected use cases. The technical challenges of parallel processing for demodulation and decoding algorithms in software will be elaborated. Based on existing implementations and partially new designs, the dedicated exploitation of hardware-specific elements is expected to achieve bandwidths of 36 MHz and beyond, matching the application-specific requirements.

Challenges

There are two main technical challenges connected to the design of a real-time software demodulator:

-

In the first place, several algorithms traditionally oriented to hardware implementations have to be adapted to a software paradigm. This is particularly challenging due to the variable frame size used in the DVB-S2X physical layer.

-

On a more implementation-oriented basis, the features offered by the hardware platform (e.g., SIMD instruction set extensions) shall be intensively exploited.

System Architecture

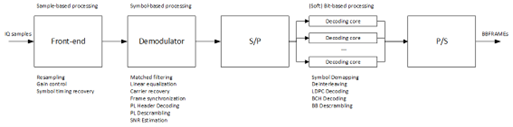

The architecture of the SWDM is implicitly dictated by the data types and rates which shall be processed at each step.

A combination of pipelining and parallelism is employed to leverage the constraints of the specific algorithmic blocks. This is facilitated by the underlying software platform, which is a modular single-process multi-threaded system, where the individual threads can have an affinity to a specific processor core as per the needs of the software.

A highly simplified overview of the receiver architecture is shown below.

Plan

The project followed a familiar waterfall project process:

-

System Requirements Review, Q1 2022: Definition of applications and requirements, State-of-the-Art analysis, Creation of technical specification & Outline verification plan

-

Preliminary Design Review, Q3 2022: Select a Technical baseline selection & establish a Preliminary Design

-

Critical Design Review, Q1 2023: Establish a Detailed Design, Integration Plan and Test Plan

-

Test Readiness Review, Q2 2024: Implementation of the deliverable Items and first test runs.

-

Final Acceptance Review, Q4 2024: Final Review and perform critical assessment of potential of developed items for commercial exploitation

Current Status

The activity has achieved the Final Acceptance Review (FAR).

The public final presentation is scheduled for the ARTES Final Presentation Days 2025.