PAGE CONTENTS

Objectives

Main Objectives of this activity are

- the development of the multiMIND signal processing core with the following characteristics:

- based on high performance COTS components, combined with reliable rad-hard supervisor to ensure robustness under space conditions

- prepared to be used as SDR core for a multitude of mission and payload use-cases such as IoT, SATCOM, AIS, ADS-B, EO and spectrum monitoring.

- available as stand-alone product and integrated in full payload solutions

- prepared to be complemented by mission specific elements enabling flexibility w.r.t. customer needs by ensuring cost-sensitive developments to remain in the generic element multiMIND

- the in-orbit demonstration as payload data processor on the cubesat mission EIVE (Exploratory In-Orbit Verification of an E/W-Band Satellite Communication Link) developed, built and operated by the University of Stuttgart and funded by DLR.

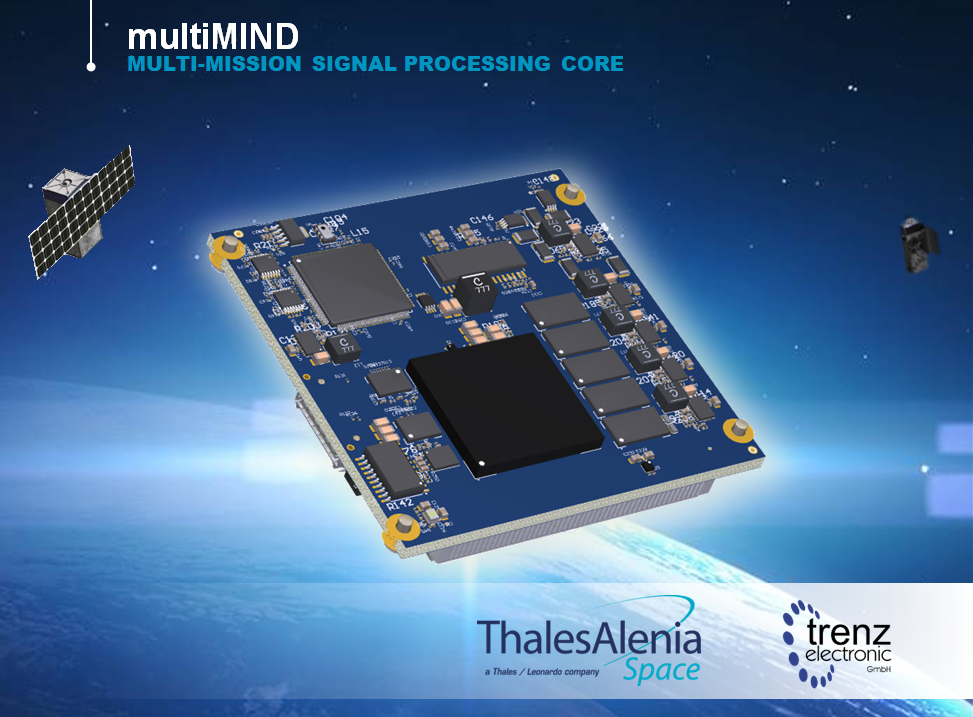

multiMIND processing core

Challenges

Key challenge of this development is to enable a safe operation of latest MPSoC chip technology in space and to build a cubesat-ready product, which can be efficiently used for a variety of different mission profiles requiring efficient processing capabilities.

System Architecture

Seeing the need of a reliable usage of high performance COTS parts, multiMIND consists out of 2 functional domains:

- Non-vital function domain

- High computational power needed,

- Has to survive SEE, but short outages (resets) are acceptable.

- Essential function domain

- Low resource usage,

- Outage-free operation required.

Non-vital functions can benefit from the performance of COTS hardware as well as COTS software and firmware. Essential functions are implemented using rad-hard space components.

Plan

ARTES C&G Product and Demo Phase Kick-off: August 2020

Critical Design Review and EM testing: September 2020

Flight Hardware delivery: Apr 2021

Satellite Launch: second half of 2021

In-Orbit Demonstration: 2021/2022

Current Status

Definition Phase and Technology Phase have been successfully completed. These included feasibility study, requirements consolidation and several derisking activities (e.g. hardware breadboarding and software prototyping) to prepare for an efficient and fast Development Phase.

Development Phase has started in early 2020 anticipating the present ESA project formally launched in August 2020. Currently EM built-up is ongoing in parallel to CDR preparation.